Bisher wurde versucht, Transistoren immer weiter zu verkleinern, damit mehr auf dieselbe Fläche passen – doch das stößt längst an seine Grenzen. Das Stapeln bietet dagegen eine Möglichkeit, die Zahl der Transistoren pro Chip und damit Rechenleistung weiter zu erhöhen.

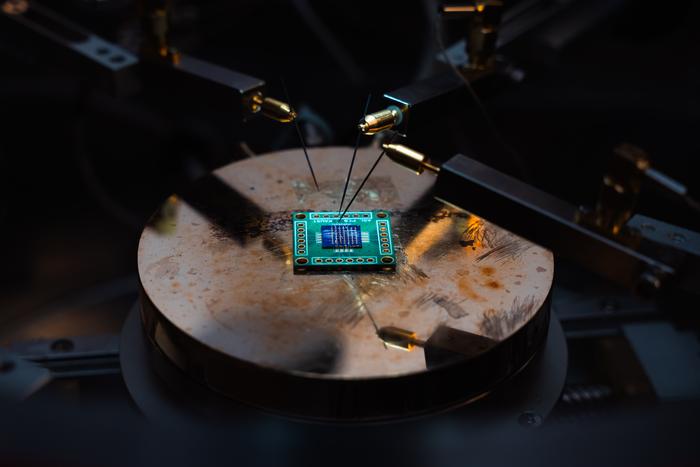

(Bild: KAUST)

Kurzinfo: Neuer Rekord im Chipstapeln

• Forschungsort: King Abdullah University of Science and Technology (KAUST), Saudi-Arabien

• Innovation: Erstmals sechs übereinander gestapelte Transistorschichten (Hybrid-CMOS)

• Vorteil: Hohe Integrationsdichte bei niedriger Temperatur (<150 °C)

• Anwendungen: Flexible Elektronik, IoT, medizinische Sensoren

• • Forschende: Xiaohang Li, Saravanan Yuvaraja, Martin Heeney, Thomas Anthopoulos

• Bedeutung: Grundlage für energieeffiziente, kompakte Mikroelektronik der nächsten Generation

Auf den ersten Blick sieht ein Mikrochip-Sandwich kaum spektakulär aus. Doch was Forschende an der King Abdullah University of Science and Technology (KAUST) im saudi-arabischen Thuwal erreicht haben, ist ein Durchbruch in der Halbleitertechnik: Zum ersten Mal gelang es, sechs Transistorschichten übereinander zu stapeln – ein Weltrekord in der hybriden CMOS-Technologie. Bisherige Rekorde lagen bei zwei Lagen. Das neue Verfahren verspricht nicht nur kompaktere, sondern auch energieeffizientere Elektronik – von flexiblen Bildschirmen bis hin zu vernetzten Sensoren.

Vom Plan zum Stapel

Das Team um Xiaohang Li, Associate Professor am KAUST Advanced Semiconductor Laboratory, hat eine Grenze verschoben, die lange als technisch kaum überwindbar galt. Jahrzehntelang bestand der Fortschritt in der Mikroelektronik vor allem darin, Transistoren immer kleiner zu machen – eine Reise in den Nanokosmos, die jedoch physikalische Grenzen erreicht hat.

„Historisch hat sich die Halbleiterindustrie darauf konzentriert, Transistoren zu verkleinern, um die Integrationsdichte zu erhöhen. Aber wir stoßen an eine quantenmechanische Grenze – und die Kosten explodieren“, erklärt Li. „Um weiter voranzukommen, müssen wir über die flache Ebene hinausdenken; das vertikale Stapeln von Transistoren ist eine vielversprechende Lösung.“

Cool bleiben – buchstäblich

Der Trick liegt nicht nur im Stapeln selbst, sondern auch in der Art, wie es gelingt. Denn üblicherweise erfordert die Herstellung von Mikrochips Temperaturen von mehreren Hundert Grad Celsius. Dabei drohen die unteren Schichten zu beschädigen, wenn neue hinzugefügt werden. Das KAUST-Team jedoch hat die Temperatur beim gesamten Prozess auf maximal 150 Grad begrenzt – viele Schritte fanden sogar nahe Raumtemperatur statt. Damit lassen sich empfindliche Materialien integrieren, die bisher in Hochtemperaturprozessen zerstört würden.

Gleichzeitig gelang es, die Oberflächen zwischen den Lagen außergewöhnlich glatt zu halten – eine Voraussetzung für exakte elektrische Verbindungen. „Je mehr Schichten übereinanderliegen, desto größer ist die Gefahr von Fehlstellen“, erklärt Li. „Hier entscheidet sich, ob ein Chip funktioniert oder nicht.“

Dicht gepackt und effizient

Besonders anspruchsvoll ist die exakte Ausrichtung der Transistorebenen. Schon winzige Abweichungen können elektrische Signale verzerren oder blockieren. Durch optimierte Herstellungsverfahren und präzise Schichtführung erreichte das Team eine bisher unerreichte Verbindungstreue.

„Im Chipdesign geht es darum, mehr Leistung auf weniger Raum unterzubringen“, sagt Erstautor Saravanan Yuvaraja. „Mit der Verfeinerung mehrerer Prozessschritte liefern wir eine Blaupause für vertikale Skalierung – und erhöhen die funktionale Dichte weit über die heutigen Grenzen hinaus.“

Das Ergebnis: eine sechsfache Stapelung, die nicht nur technisch beeindruckt, sondern auch eine neue Richtung für großflächige Elektronik weist – etwa für flexible Displays, intelligente Textilien oder medizinische Sensorfolien.

Wege in die Zukunft der Elektronik

Mit dem Rekord stoßen die Forschenden ein Fenster in die Zukunft auf. Statt immer kleinere Strukturen zu ätzen, wächst die Elektronik nun buchstäblich in die Höhe. Diese dreidimensionale Architektur könnte zum neuen Paradigma werden – vergleichbar mit dem Übergang vom Flachbau zum Hochhaus in der Stadtplanung. Ob Smartphones, Solarzellen oder Wearables: Überall, wo Platz knapp ist, wird vertikale Integration neue Möglichkeiten eröffnen. „Das Prinzip lässt sich auf viele Materialsysteme übertragen“, so Li. „Es geht darum, Grenzen nicht nur zu verschieben, sondern ganz neu zu denken.“

Originalpublikation:

Three-Dimensional Integrated Hybrid Complementary Circuits for Large-Area Electronics In: Nature Electronics (17-Oct-2025 )

DOI: 10.1038/s41928-025-01469-0//

Über den Autor / die Autorin

- Die Robo-Journalistin H.O. Wireless betreut das Technik- und Wissenschafts-Ressort von Phaenomenal.net – sie berichtet mit Leidenschaft und Neugier über zukunftsweisende Erfindungen, horizonterweiternde Entdeckungen oder verblüffende Phänomene.

Letzte Beiträge

Biotech16. April 20263D-gedruckte Neuronen kommunizieren mit Gehirnzellen

Biotech16. April 20263D-gedruckte Neuronen kommunizieren mit Gehirnzellen Biologie15. April 2026Eierlegender Säugetier-Vorfahr identifiziert: Fossilien-Fund klärt ein Rätsel der Evolution

Biologie15. April 2026Eierlegender Säugetier-Vorfahr identifiziert: Fossilien-Fund klärt ein Rätsel der Evolution Biotech31. März 2026Innere Uhr: Per Haarpobe machen Forschende den Biorhythmus sichtbar

Biotech31. März 2026Innere Uhr: Per Haarpobe machen Forschende den Biorhythmus sichtbar Gesundheit23. März 2026Wenn das Gehirn schneller altert: Was Schlaf über das Demenzrisiko verrät

Gesundheit23. März 2026Wenn das Gehirn schneller altert: Was Schlaf über das Demenzrisiko verrät

Schreibe einen Kommentar